- 您现在的位置:买卖IC网 > Sheet目录985 > ISLA224IR72EV1Z (Intersil)BOARD EVALUATION FOR ISLA224P

�� �

�

�

�ISLA224P�

�Data� Format�

�Output� data� can� be� presented� in� three� formats:� two’s�

�complement(default),� Gray� code� and� offset� binary.� The� data�

�Mapping� of� the� input� voltage� to� the� various� data� formats� is�

�shown� in� Table� 3.�

�TABLE� 3.� INPUT� VOLTAGE� TO� OUTPUT� CODE� MAPPING�

�format� can� also� be� controlled� through� the� SPI� port,� by� writing� to�

�address� 0x73.� Details� on� this� are� contained� in� “Serial� Peripheral�

��INPUT�

�VOLTAGE�

�OFFSET� BINARY�

�TWO’S�

�COMPLEMENT�

�GRAY� CODE�

�Offset� binary� coding� maps� the� most� negative� input� voltage� to�

�code� 0x000� (all� zeros)� and� the� most� positive� input� to� 0xFFF� (all�

�ones).� Two’s� complement� coding� simply� complements� the� MSB�

�of� the� offset� binary� representation.�

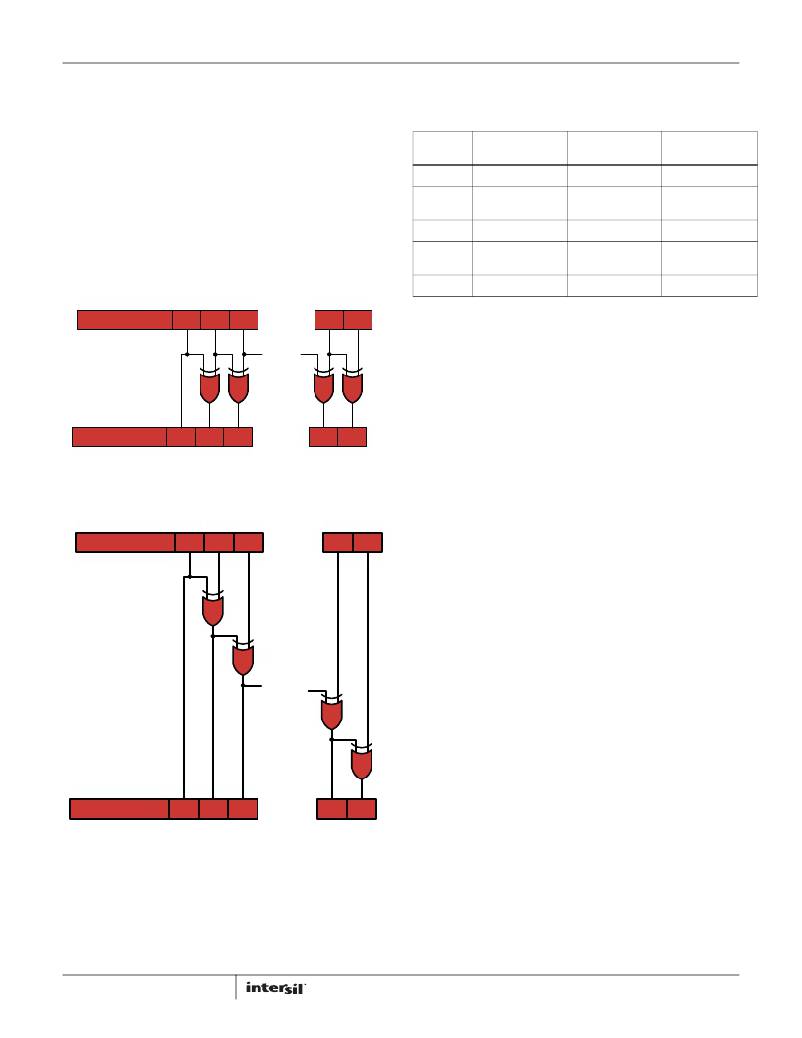

�When� calculating� Gray� code� the� MSB� is� unchanged.� The�

�remaining� bits� are� computed� as� the� XOR� of� the� current� bit�

�position� and� the� next� most� significant� bit.� Figure� 35� shows� this�

�operation.�

�–Full� Scale� 00� 0000� 0000� 0000� 10� 0000� 0000� 0000� 00� 0000� 0000� 0000�

�–Full� Scale� 00� 0000� 0000� 0001� 10� 0000� 0000� 0001� 00� 0000� 0000� 0001�

�+� 1LSB�

�Mid–Scale� 10� 0000� 0000� 0000� 00� 0000� 0000� 0000� 11� 0000� 0000� 0000�

�+Full� Scale� 11� 1111� 1111� 1110� 01� 1111� 1111� 1110� 10� 0000� 0000� 0001�

�–� 1LSB�

�+Full� Scale� 11� 1111� 1111� 1111� 01� 1111� 1111� 1111� 10� 0000� 0000� 0000�

�BINARY�

�13�

�12�

�11�

�????�

�1�

�0�

�Clock� Divider� Synchronous� Reset�

�If� the� selectable� clock� divider� is� used,� the� ADC's� internal� sample�

�clock� will� be� at� half� the� frequency� (DIV� =� 2)� or� one� quarter� the�

�frequency� (DIV� =� 4)� of� the� device� clock.� The� phase� relationship�

�????�

�between� the� sample� clock� and� the� device� clock� is� initially�

�indeterminate.� An� output� clock� (CLKOUTP,� CLKOUTN)� is� provided�

�to� facilitate� latching� of� the� sampled� data� and� estimation� of� the�

�internal� sample� clock's� phase.� The� output� clock� has� a� fixed�

�GRAY� CODE�

�13�

�12�

�11�

�????�

�1�

�0�

�phase� relationship� to� the� sample� clock.� When� the� selectable�

�FIGURE� 35.� BINARY� TO� GRAY� CODE� CONVERSION�

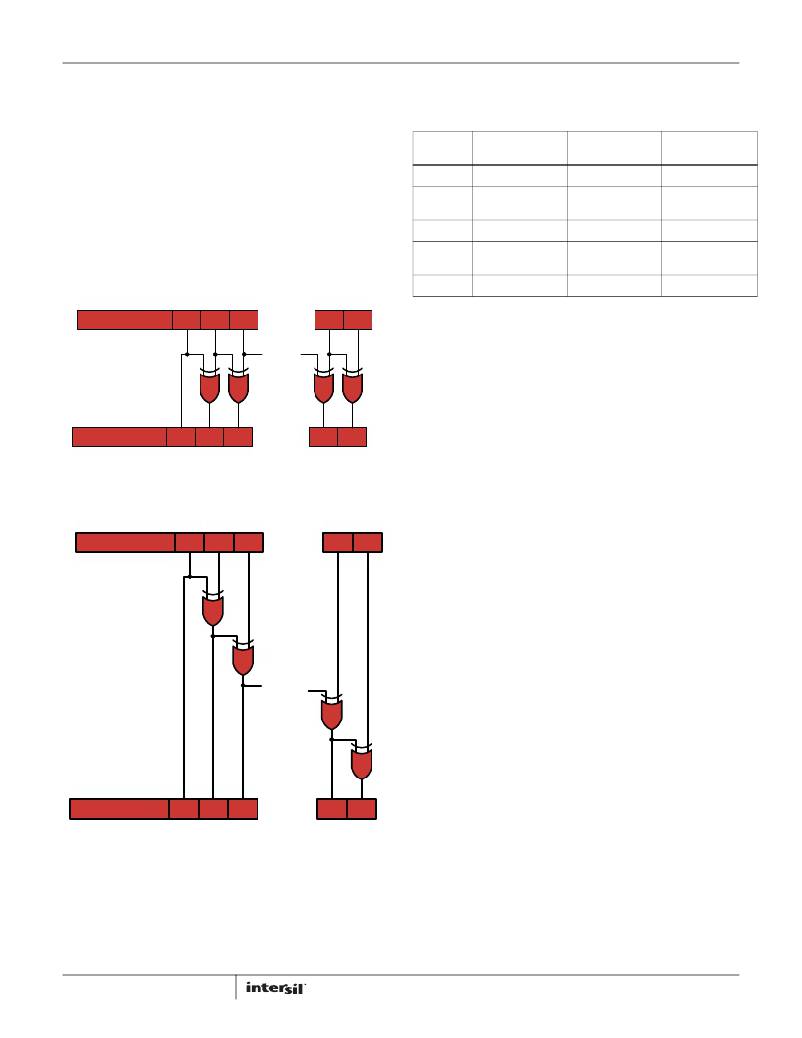

�Converting� back� to� offset� binary� from� Gray� code� must� be� done�

�recursively,� using� the� result� of� each� bit� for� the� next� lower� bit� as�

�shown� in� Figure� 36.�

�clock� divider� is� set� to� 2� or� 4,� the� output� clock's� phase� relationship�

�to� the� sample� clock� remains� fixed� but� is� initially� indeterminate�

�with� respect� to� the� device� clock.� When� the� selectable� clock�

�divider� is� set� to� 2� or� 4,� the� synchronous� clock� divider� reset�

�feature� allows� the� phase� of� the� internal� sample� clock� and� the�

�output� clock� to� be� synchronized� (refer� to� Figure� 37)� with� respect�

�GRAY� CODE�

�13�

�12�

�11�

�????�

�1�

�0�

�to� the� device� clock.� This� simplifies� data� capture� in� systems�

�employing� multiple� A/Ds� where� sampling� of� the� inputs� is� desired�

�to� be� synchronous.�

�The� reset� signal� must� be� well-timed� with� respect� to� the� sample�

�clock� (See� “Switching� Specifications”� on� page� 12).�

�????�

�A� 100� ?� differential� termination� resistor� must� be� supplied�

�between� CLKDIVRSTP� and� CLKDIVRSTN,� external� to� the� ADC,� (on�

�the� PCB)� and� should� be� located� as� close� to� the� CLKDIVRSTP/N�

�pins� as� possible.�

�????�

�BINARY�

�13�

�12�

�11�

�????�

�1�

�0�

�FIGURE� 36.� GRAY� CODE� TO� BINARY� CONVERSION�

�21�

�FN7570.1�

�November� 30,� 2012�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISPTPKIT

SCREW KIT TAMPER RESISTANT 9PCS

ITCSN-0400-25-U

HEATSHRINK ITCSN 2/5" X 25'

JC2AF-TM-DC24V-F

RELAY GEN PURPOSE DPST 10A 24V

JJM1A-12V

RELAY AUTOMOTIVE SPST 20A 12V

JM1AN-ZTM-DC5V-F

RELAY GEN PURPOSE SPST 20A 5V

JQ1P-18V-F

RELAY GEN PURPOSE SPDT 10A 18V

JS1-F-6V-F

RELAY GEN PURPOSE SPDT 10A 6V

JSM1-9V-5

RELAY AUTOMOTIVE SPDT 15A 9V

相关代理商/技术参数

ISLA224P

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance Dual 14-Bit, 125MSPS ADC

ISLA224P12IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 125MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SPI/SRL 125M 48QFN 制造商:Intersil 功能描述:Dual 14-Bit 125MSPS Unbuffered Input, 72

ISLA224P13

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P13IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 130MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SRL/SPI 72QFN 制造商:Intersil 功能描述:DL 14-BIT 130MSPS UNBUFRED INPUT 72PIN

ISLA224P20

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P20IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 200MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SRL/SPI 72QFN 制造商:Intersil 功能描述:DL 14-BIT 200MSPS UNBUFRED INPUT 72PIN 制造商:Intersil Corporation 功能描述:IC, ADC, 14BIT; Resolution (Bits):14bit; Sampling Rate:200MSPS; Supply Voltage Type:Single; Supply Voltage Min:1.7V; Supply Voltage Max:1.9V; Supply Current:375mA; Digital IC Case Style:QFN; No. of Pins:72; Data Interface:SPI ;RoHS Compliant: Yes

ISLA224P25

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC